Part 1: Background and Reverse Engineering the BLEs

Contents

- CLB Background

- Digging into the Datasheet

- Digging into the tool

- Digging into the backend files

- Decoding the BLE LUT Configuration

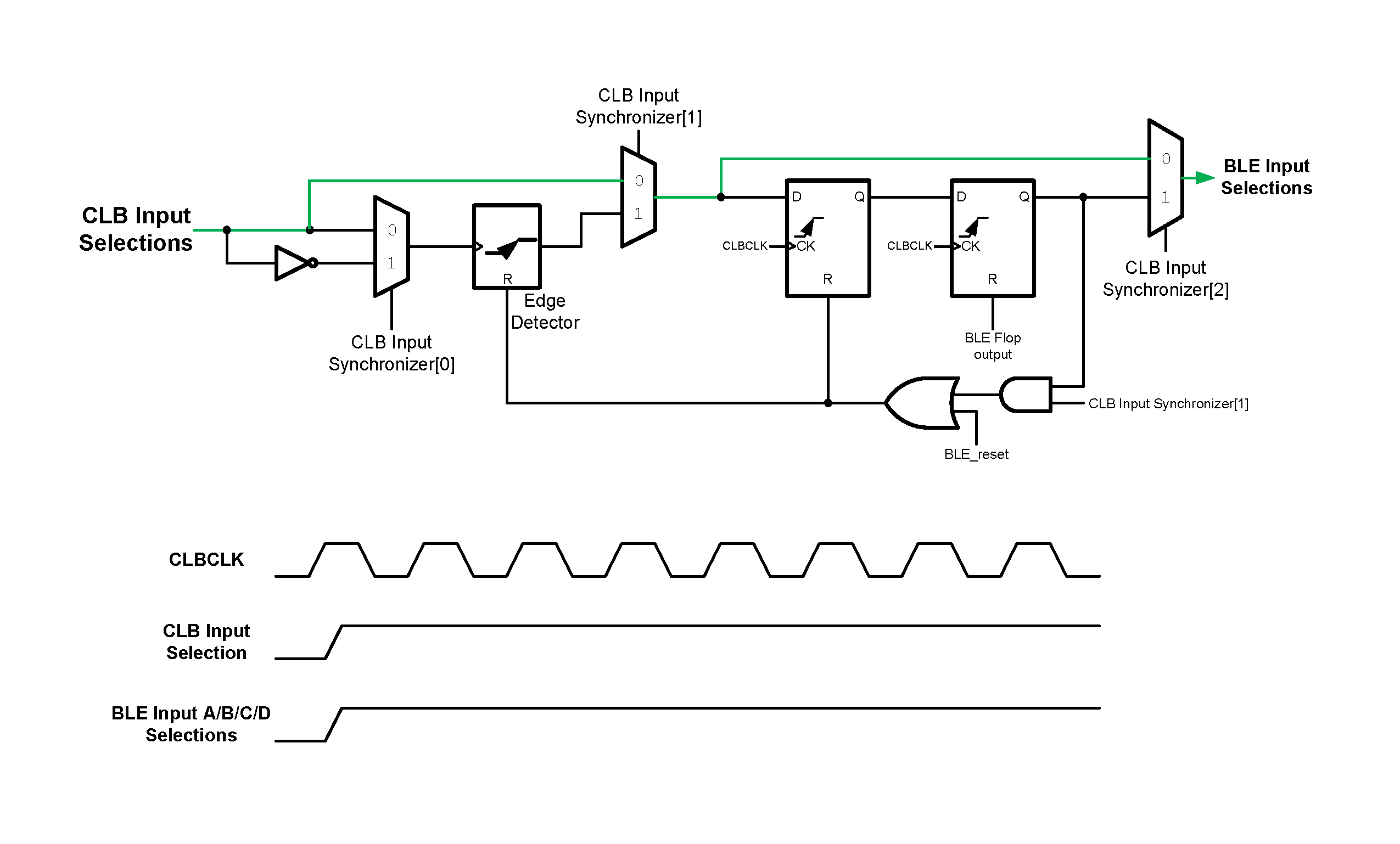

- Decoding the BLE LUT Input Configuration

- FLOPSEL

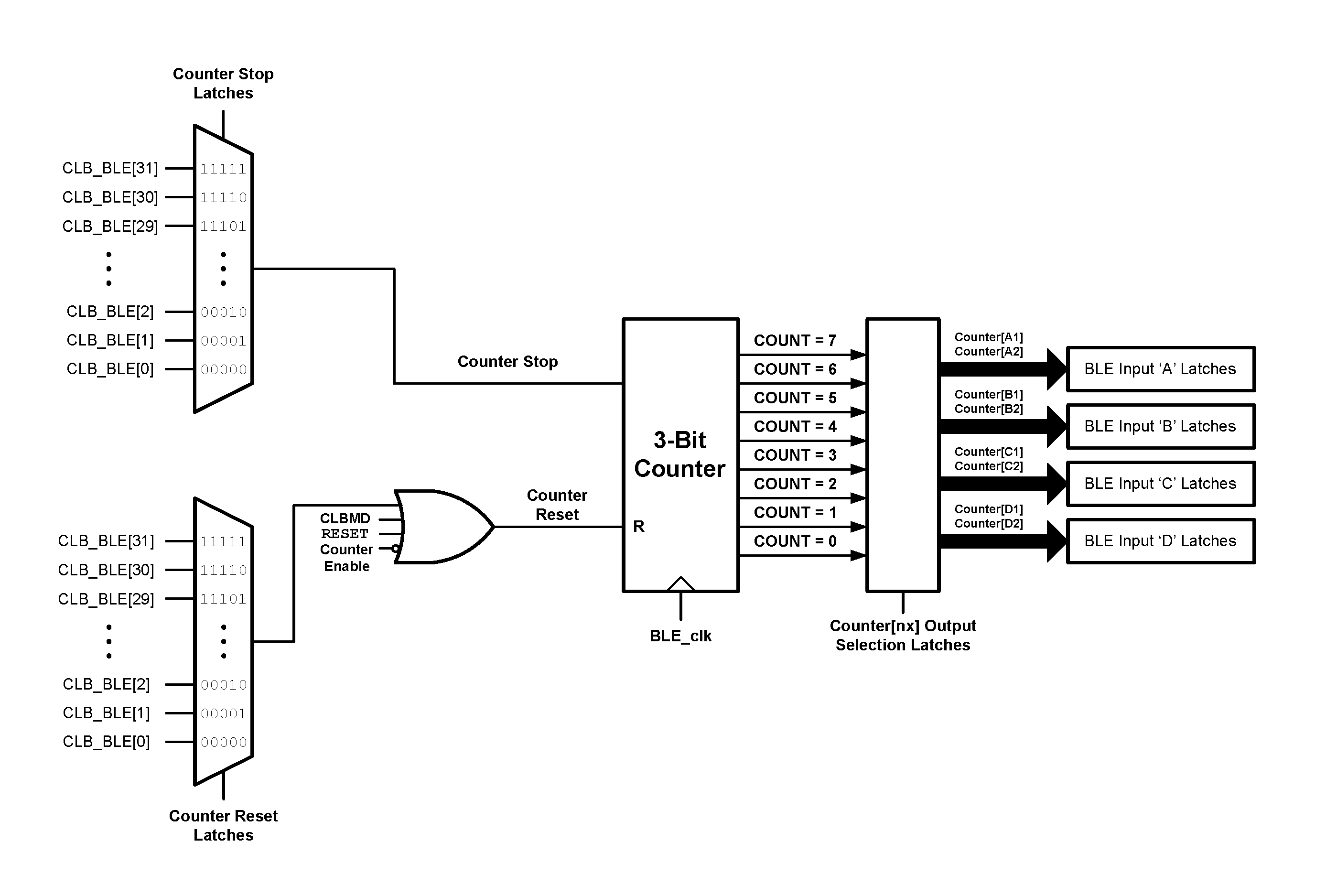

- Counter

- Inputs

- Outputs

- CLKDIV

- Final Config Table

CLB Background

The datasheet tells us that the CLB has 32 Basic Logic Elements (BLEs) that each have Look-Up Tables (LUTs). I generally use the terms interchangeably throughout this series of posts.

What is a LUT?

A LUT is the basic building block of an FPGA, it looks up a result based on the given input. The CLB uses a 4-LUT, a LUT with 4 inputs, as its base element.

A LUT does what it says on the box: based on the 4 inputs, it looks up an output value. It can be used to implement any 4-input boolean function, i.e., AND/OR/XOR/NOR, or even complex functions like an AND gate with the second input inverted and the third input overriding the 4th.

LUTs are typically also included with a latch, so they can be configured as various types of latches/flip-flops. When configured like this, it’s generally called a Basic Logic Element (BLE).

Digging into the Datasheet

The first step on our journey is to see what information Microchip does provide us about how the CLB works and what’s inside!.

Microchip’s Basic Logic Element

The first stop is there diagram of what’s inside a BLE:

Source: Microchip, PIC16F13145 Datasheet

Microchip’s BLE has a standard 4-input LUT with a D flip-flop. In the CLB, each BLE shares most of the inputs shown above. CLBCLK is a global input to the CLB peripheral; CLBMD/RESET/EN are all for the whole module.

Only the BLE Input A/B/C/D and the BLE Flop select are per BLE as well as the LUT config itself.

We can start our definition of what makes up the CLB (the Data Model) with this defining a python dataclass to hold our BLE config:

@dataclass

class BLE_CFG:

LUT_CONFIG: int # 16-bit

FLOPSEL: bool

LUT_I_A: LUT_IN_A

LUT_I_B: LUT_IN_B

LUT_I_C: LUT_IN_C

LUT_I_D: LUT_IN_D

BLE Input Selection

Next, they have an extremely helpful diagram showing what can be connected to every BLE input:

Source: Microchip, PIC16F13145 Datasheet

A couple of things to note:

- Each LUT input configuration is 5 bits for a total of 20 bits of configuration for the BLE inputs.

- The

CLB_BLE[n]values are from the specified BLE, and not every BLE can go to every LUT input. This hints at the physical layout of the BLEs on the chip. - The

CLB_IN_SYNC[n]inputs come from the 16 CLB module input signals (more on those later). - The

COUNTER[n]inputs are from the built-in counter peripheral in the CLB (more on it later).

But luckily Microchip provides what the mappings from bits to inputs! This would have been a major pain to reverse engineer.

Let’s add it to our data model:

class LUT_IN_A(IntEnum):

"""BLE INPUT A[4:0]"""

CLB_BLE_0 = 0b00000

CLB_BLE_1 = 0b00001

CLB_BLE_2 = 0b00010

CLB_BLE_3 = 0b00011

# ...

CLBSWIN7 = 0b10011

COUNT_IS_A1 = 0b10100

COUNT_IS_A2 = 0b10101

# ...

Full BLE Input Data Model

For the eagle-eyed among you, you will notice I use IN0 below vs. the above CLB_IN_SYNC. The reason will become apparent later.

class LUT_IN_A(IntEnum):

"""BLE INPUT A[4:0]"""

CLB_BLE_0 = 0b00000

CLB_BLE_1 = 0b00001

CLB_BLE_2 = 0b00010

CLB_BLE_3 = 0b00011

CLB_BLE_4 = 0b00100

CLB_BLE_5 = 0b00101

CLB_BLE_6 = 0b00110

CLB_BLE_7 = 0b00111

IN0 = 0b01000

IN1 = 0b01001

IN2 = 0b01010

IN3 = 0b01011

CLBSWIN0 = 0b01100

CLBSWIN1 = 0b01101

CLBSWIN2 = 0b01110

CLBSWIN3 = 0b01111

CLBSWIN4 = 0b10000

CLBSWIN5 = 0b10001

CLBSWIN6 = 0b10010

CLBSWIN7 = 0b10011

COUNT_IS_A1 = 0b10100

COUNT_IS_A2 = 0b10101

class LUT_IN_B(IntEnum):

"""BLE INPUT B[4:0]"""

CLB_BLE_8 = 0b00000

CLB_BLE_9 = 0b00001

CLB_BLE_10 = 0b00010

CLB_BLE_11 = 0b00011

CLB_BLE_12 = 0b00100

CLB_BLE_13 = 0b00101

CLB_BLE_14 = 0b00110

CLB_BLE_15 = 0b00111

IN4 = 0b01000

IN5 = 0b01001

IN6 = 0b01010

IN7 = 0b01011

CLBSWIN8 = 0b01100

CLBSWIN9 = 0b01101

CLBSWIN10 = 0b01110

CLBSWIN11 = 0b01111

CLBSWIN12 = 0b10000

CLBSWIN13 = 0b10001

CLBSWIN14 = 0b10010

CLBSWIN15 = 0b10011

COUNT_IS_B1 = 0b10100

COUNT_IS_B2 = 0b10101

class LUT_IN_C(IntEnum):

"""BLE INPUT C[4:0]"""

CLB_BLE_16 = 0b00000

CLB_BLE_17 = 0b00001

CLB_BLE_18 = 0b00010

CLB_BLE_19 = 0b00011

CLB_BLE_20 = 0b00100

CLB_BLE_21 = 0b00101

CLB_BLE_22 = 0b00110

CLB_BLE_23 = 0b00111

IN8 = 0b01000

IN9 = 0b01001

IN10 = 0b01010

IN11 = 0b01011

CLBSWIN16 = 0b01100

CLBSWIN17 = 0b01101

CLBSWIN18 = 0b01110

CLBSWIN19 = 0b01111

CLBSWIN20 = 0b10000

CLBSWIN21 = 0b10001

CLBSWIN22 = 0b10010

CLBSWIN23 = 0b10011

COUNT_IS_C1 = 0b10100

COUNT_IS_C2 = 0b10101

class LUT_IN_D(IntEnum):

"""BLE INPUT D[4:0]"""

CLB_BLE_24 = 0b00000

CLB_BLE_25 = 0b00001

CLB_BLE_26 = 0b00010

CLB_BLE_27 = 0b00011

CLB_BLE_28 = 0b00100

CLB_BLE_29 = 0b00101

CLB_BLE_30 = 0b00110

CLB_BLE_31 = 0b00111

IN12 = 0b01000

IN13 = 0b01001

IN14 = 0b01010

IN15 = 0b01011

CLBSWIN24 = 0b01100

CLBSWIN25 = 0b01101

CLBSWIN26 = 0b01110

CLBSWIN27 = 0b01111

CLBSWIN28 = 0b10000

CLBSWIN29 = 0b10001

CLBSWIN30 = 0b10010

CLBSWIN31 = 0b10011

COUNT_IS_D1 = 0b10100

COUNT_IS_D2 = 0b10101Digging into the tool

The next step is to start poking around at the tool Microchip provides for configuring the CLB.

CLB Synthesizer

Source: Microchip, CLB Synthesizer

It’s called CLB Synthesizer. You can use their web version or the version that gets auto-installed by MPLAB X (their IDE); it turns out it’s just an NPM module. It is a drag and drop interface that lets you build logic designs and translate them into the corresponding CLB configuration.

How Does it Work?

CLB Synthesizer lets you build your circuit in its drag-and-drop interface (optionally also with a Verilog module), and the web frontend generates some Verilog and corresponding supporting files.

For example, the inverter example above generates the files shown below. Let’s dig in.

Verilog

The first file is the main.v file that contains the body of the module you designed.

(* MUX0.CLBIN = 6'd0 *)

(* MUX0.INSYNC = 3'b100 *)

(* CLKDIV = 3'd1 *)

module main

(CLBIN0PPS_synchronized, PPS_OUT1);

input CLBIN0PPS_synchronized;

output PPS_OUT1;

logic net2;

not U1 (net2, CLBIN0PPS_synchronized);

assign PPS_OUT1 = net2;

endmodule

Constraints

The next file is main.xdc. It’s a constraints file that, in the CLB synthesizer, primarily specifies the names of signals,

mapping them from internal names to more user-friendly ones.

set_property PACKAGE_PIN IN0 [get_ports CLBIN0PPS_synchronized]

set_property PACKAGE_PIN PPS_OUT1 [get_ports PPS_OUT1]

Here you can see we define the signal IN0 to be named CLBIN0PPS_synchronized for use above.

Project files

The last few files are files that define the project; they map to the visual layout as well as some metadata about the design.

It does not appear to include any personal information beyond the software version used and the creation date.

design.clb

{

"backendversion": "25.3.1-4",

"clockDivider": 1,

"creationDate": "2023-09-26T12:59:39.897Z",

"device": "PIC16F13145",

"entryFile": "main",

"hdls": [

],

"mnmap": [

{

"id": "cd4ee2db-361f-4f1f-94dd-f6a50e67a83c",

"name": "main",

"type": 0

}

],

"name": "inverter",

"projectId": "6d4d6a22-1273-4bf4-a115-eed4f658bc43",

"schematics": [

{

"data": {

"class": "GraphLinksModel",

"linkDataArray": [

{

"from": 1,

"fromPort": "OUT",

"key": -1,

"points": [

-255,

-90,

-245,

-90,

-82,

-90,

-82,

-90,

-39,

-90,

-29,

-90

],

"to": 2,

"toPort": "IN1"

},

{

"from": 2,

"fromPort": "OUT",

"key": -2,

"points": [

51,

-90,

61,

-90,

153,

-90,

153,

-90,

285,

-90,

295,

-90

],

"to": 3,

"toPort": "IN"

}

],

"linkFromPortIdProperty": "fromPort",

"linkKeyProperty": "key",

"linkToPortIdProperty": "toPort",

"nodeDataArray": [

{

"category": "inputport",

"inputmodifier": "synchronized",

"key": 1,

"loc": "-320 -90",

"portname": "CLBIN0PPS",

"size": "130 20"

},

{

"category": "not",

"key": 2,

"loc": "10 -90"

},

{

"category": "outputport",

"inputmodifier": "synchronized",

"key": 3,

"loc": "360 -90",

"portname": "PPS_OUT1",

"size": "130 20"

},

{

"category": "comment",

"key": "comment",

"loc": "-200 110",

"text": "Input Port"

}

]

},

"id": "cd4ee2db-361f-4f1f-94dd-f6a50e67a83c"

}

],

"type": "Microchip CLB Synthesizer Design",

"version": "1.0"

}project.json

{

"creationDate": "2023-09-26T12:59:39.897Z",

"device": "PIC16F13145",

"interface": {

"inputs": [

"CLBIN0PPS"

],

"outputs": [

"PPS_OUT1"

]

},

"projectId": "6d4d6a22-1273-4bf4-a115-eed4f658bc43",

"topLevelFile": "main",

"type": "Microchip CLB Synthesizer Design",

"version": "0.2"

}stats.json

{

"client": "web",

"clientVersion": "1.3.0-3",

"device": "PIC16F13145",

"projectId": "6d4d6a22-1273-4bf4-a115-eed4f658bc43",

"schematics": 1,

"symbols": {

"inputport": 2,

"not": 2,

"outputport": 2

},

"verilog": 0

}Submit to Backend

The last step is to zip the files and submit them to the backend for synthesis.

Response

The backend responds with a JSON message containing a zip file that has a lot of interesting information.

{

"synthres": {

"formatversion": "0.1",

"clb": "pic16f131xx_v1",

"id": "1743199249251",

"bitstream": [

"0x3C00",

...

"0x0000"

],

"outputmappings": {},

"inputs": [

"CLBIN0PPS"

],

"outputs": [

"PPS_OUT1"

],

"resources": [

{

"type": "LUTs",

"count": 1,

"of": 32

}

],

"status": "success",

"errormessage": ""

},

"process": {

"returncode": 0,

"killed": false,

"stdout": "\nPerform synthesis:\n\n\n ...",

"stderr": ""

},

"zip": "UEsDBB..."

}

Zip content:

zip

│ bitstream.s

│ clb1.c

│ clb1.h

│ clb1_output_mappings.h

│ pre-routing.svg

│ readme.txt

│ routed.svg

│

├───build

│ bitstream.json

│ funfacts.tmp

│ out.fasm

│ out.net

│ out.net.post_routing

│ out.netlist

│ out.phys

│ out.place

│ out.route

│ packing_pin_util.rpt

│ pre-routing.dot

│ pre-routing.v

│ routed.dot

│ routed.v

│ stderr.txt

│ stdout.txt

│ synth.json

│ vpr_stdout.log

│ yosys.log

│

└───input

design.clb

main.v

main.xdc

project.json

stats.json

Lets dig in…

Digging into the backend files

We get quite a lot of information from the backend.

The first set of files we get are the outputs for you to load into the CLB on your microcontroller, including the raw bitstream:

│ bitstream.s

│ clb1.c

│ clb1.h

│ clb1_output_mappings.h

This bitstream has 102 words in it, 1428 bits to reverse engineer (this PIC has 14 bit words).

More interesting at the top level is routed.svg:

routed.svg

This tells us quite a lot, like exactly what BLE is used, what inputs it uses, how it’s configured, etc.

Next, we can take a peek at the build dir. stdout.txt, it tells us that Microchip is using the

open source Yosys design chain with custom extensions for the CLB.

stdout.txt

Perform synthesis:

/----------------------------------------------------------------------------\

| |

| yosys -- Yosys Open SYnthesis Suite |

| |

| Copyright (C) 2012 - 2020 Claire Xenia Wolf <claire@yosyshq.com> |

| |

| Permission to use, copy, modify, and/or distribute this software for any |

| purpose with or without fee is hereby granted, provided that the above |

| copyright notice and this permission notice appear in all copies. |

| |

| THE SOFTWARE IS PROVIDED "AS IS" AND THE AUTHOR DISCLAIMS ALL WARRANTIES |

| WITH REGARD TO THIS SOFTWARE INCLUDING ALL IMPLIED WARRANTIES OF |

| MERCHANTABILITY AND FITNESS. IN NO EVENT SHALL THE AUTHOR BE LIABLE FOR |

| ANY SPECIAL, DIRECT, INDIRECT, OR CONSEQUENTIAL DAMAGES OR ANY DAMAGES |

| WHATSOEVER RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN |

| ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF |

| OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THIS SOFTWARE. |

| |

\----------------------------------------------------------------------------/

Yosys 0.25 (git sha1 e02b7f64b, gcc 10.2.1-6 -fPIC -Os)

-- Running command ` read_verilog -sv -I../input ../input/main.v; synth_microchip -top main -rmports; scc; write_json synth.json' --

1. Executing Verilog-2005 frontend: ../input/main.v

Parsing SystemVerilog input from `../input/main.v' to AST representation.

Generating RTLIL representation for module `\main'.

Successfully finished Verilog frontend.

2. Executing SYNTH_MICROCHIP pass.

2.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/microchip/cells_sim.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/microchip/cells_sim.v' to AST representation.

Generating RTLIL representation for module `\DFF'.

Generating RTLIL representation for module `\LUT1'.

Generating RTLIL representation for module `\LUT2'.

Generating RTLIL representation for module `\LUT3'.

Generating RTLIL representation for module `\LUT4'.

Generating RTLIL representation for module `\CLB_COUNTER'.

Generating RTLIL representation for module `\IB'.

Generating RTLIL representation for module `\OB'.

Successfully finished Verilog frontend.

2.2. Executing HIERARCHY pass (managing design hierarchy).

2.2.1. Analyzing design hierarchy..

Top module: \main

2.2.2. Analyzing design hierarchy..

Top module: \main

Removed 0 unused modules.

2.3. Executing PROC pass (convert processes to netlists).

2.3.1. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.3.2. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

Removed a total of 0 dead cases.

2.3.3. Executing PROC_PRUNE pass (remove redundant assignments in processes).

Removed 0 redundant assignments.

Promoted 0 assignments to connections.

2.3.4. Executing PROC_INIT pass (extract init attributes).

2.3.5. Executing PROC_ARST pass (detect async resets in processes).

2.3.6. Executing PROC_ROM pass (convert switches to ROMs).

Converted 0 switches.

2.3.7. Executing PROC_MUX pass (convert decision trees to multiplexers).

2.3.8. Executing PROC_DLATCH pass (convert process syncs to latches).

2.3.9. Executing PROC_DFF pass (convert process syncs to FFs).

2.3.10. Executing PROC_MEMWR pass (convert process memory writes to cells).

2.3.11. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.3.12. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.4. Executing FLATTEN pass (flatten design).

2.5. Executing DEMINOUT pass (demote inout ports to input or output).

2.6. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

Removed 0 unused cells and 1 unused wires.

<suppressed ~1 debug messages>

2.8. Executing CHECK pass (checking for obvious problems).

Checking module main...

Found and reported 0 problems.

2.9. Executing OPT pass (performing simple optimizations).

2.9.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.9.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.9.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \main..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.9.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \main.

Performed a total of 0 changes.

2.9.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.9.6. Executing OPT_DFF pass (perform DFF optimizations).

2.9.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.9.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.9.9. Finished OPT passes. (There is nothing left to do.)

2.10. Executing FSM pass (extract and optimize FSM).

2.10.1. Executing FSM_DETECT pass (finding FSMs in design).

2.10.2. Executing FSM_EXTRACT pass (extracting FSM from design).

2.10.3. Executing FSM_OPT pass (simple optimizations of FSMs).

2.10.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.10.5. Executing FSM_OPT pass (simple optimizations of FSMs).

2.10.6. Executing FSM_RECODE pass (re-assigning FSM state encoding).

2.10.7. Executing FSM_INFO pass (dumping all available information on FSM cells).

2.10.8. Executing FSM_MAP pass (mapping FSMs to basic logic).

2.11. Executing OPT pass (performing simple optimizations).

2.11.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.11.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.11.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \main..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.11.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \main.

Performed a total of 0 changes.

2.11.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.11.6. Executing OPT_DFF pass (perform DFF optimizations).

2.11.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.11.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.11.9. Finished OPT passes. (There is nothing left to do.)

2.12. Executing WREDUCE pass (reducing word size of cells).

2.13. Executing PEEPOPT pass (run peephole optimizers).

2.14. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.15. Executing TECHMAP pass (map to technology primitives).

2.15.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/cmp2lut.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/cmp2lut.v' to AST representation.

Generating RTLIL representation for module `\_90_lut_cmp_'.

Successfully finished Verilog frontend.

2.15.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~6 debug messages>

2.16. Executing SHARE pass (SAT-based resource sharing).

2.17. Executing OPT pass (performing simple optimizations).

2.17.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.17.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.17.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \main..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.17.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \main.

Performed a total of 0 changes.

2.17.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.17.6. Executing OPT_DFF pass (perform DFF optimizations).

2.17.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.17.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.17.9. Finished OPT passes. (There is nothing left to do.)

2.18. Executing MEMORY pass.

2.18.1. Executing OPT_MEM pass (optimize memories).

Performed a total of 0 transformations.

2.18.2. Executing OPT_MEM_PRIORITY pass (removing unnecessary memory write priority relations).

Performed a total of 0 transformations.

2.18.3. Executing OPT_MEM_FEEDBACK pass (finding memory read-to-write feedback paths).

2.18.4. Executing MEMORY_BMUX2ROM pass (converting muxes to ROMs).

2.18.5. Executing MEMORY_DFF pass (merging $dff cells to $memrd).

2.18.6. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.18.7. Executing MEMORY_SHARE pass (consolidating $memrd/$memwr cells).

2.18.8. Executing OPT_MEM_WIDEN pass (optimize memories where all ports are wide).

Performed a total of 0 transformations.

2.18.9. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.18.10. Executing MEMORY_COLLECT pass (generating $mem cells).

2.19. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.20. Executing OPT pass (performing simple optimizations).

2.20.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.20.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.20.3. Executing OPT_DFF pass (perform DFF optimizations).

2.20.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.20.5. Finished fast OPT passes.

2.21. Executing MEMORY_MAP pass (converting memories to logic and flip-flops).

2.22. Executing OPT pass (performing simple optimizations).

2.22.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.22.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.22.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \main..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.22.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \main.

Performed a total of 0 changes.

2.22.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.22.6. Executing OPT_SHARE pass.

2.22.7. Executing OPT_DFF pass (perform DFF optimizations).

2.22.8. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.22.9. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.22.10. Finished OPT passes. (There is nothing left to do.)

2.23. Executing TECHMAP pass (map to technology primitives).

2.23.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/techmap.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/techmap.v' to AST representation.

Generating RTLIL representation for module `\_90_simplemap_bool_ops'.

Generating RTLIL representation for module `\_90_simplemap_reduce_ops'.

Generating RTLIL representation for module `\_90_simplemap_logic_ops'.

Generating RTLIL representation for module `\_90_simplemap_compare_ops'.

Generating RTLIL representation for module `\_90_simplemap_various'.

Generating RTLIL representation for module `\_90_simplemap_registers'.

Generating RTLIL representation for module `\_90_shift_ops_shr_shl_sshl_sshr'.

Generating RTLIL representation for module `\_90_shift_shiftx'.

Generating RTLIL representation for module `\_90_fa'.

Generating RTLIL representation for module `\_90_lcu'.

Generating RTLIL representation for module `\_90_alu'.

Generating RTLIL representation for module `\_90_macc'.

Generating RTLIL representation for module `\_90_alumacc'.

Generating RTLIL representation for module `\$__div_mod_u'.

Generating RTLIL representation for module `\$__div_mod_trunc'.

Generating RTLIL representation for module `\_90_div'.

Generating RTLIL representation for module `\_90_mod'.

Generating RTLIL representation for module `\$__div_mod_floor'.

Generating RTLIL representation for module `\_90_divfloor'.

Generating RTLIL representation for module `\_90_modfloor'.

Generating RTLIL representation for module `\_90_pow'.

Generating RTLIL representation for module `\_90_pmux'.

Generating RTLIL representation for module `\_90_demux'.

Generating RTLIL representation for module `\_90_lut'.

Successfully finished Verilog frontend.

2.23.2. Continuing TECHMAP pass.

Using extmapper simplemap for cells of type $not.

No more expansions possible.

<suppressed ~72 debug messages>

2.24. Executing OPT pass (performing simple optimizations).

2.24.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.24.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.24.3. Executing OPT_DFF pass (perform DFF optimizations).

2.24.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.24.5. Finished fast OPT passes.

2.25. Executing DFFLEGALIZE pass (convert FFs to types supported by the target).

2.26. Executing OPT pass (performing simple optimizations).

2.26.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.26.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.26.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \main..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.26.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \main.

Performed a total of 0 changes.

2.26.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.26.6. Executing OPT_DFF pass (perform DFF optimizations).

2.26.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.26.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.26.9. Finished OPT passes. (There is nothing left to do.)

2.27. Executing ABC9 pass.

2.27.1. Executing ABC9_OPS pass (helper functions for ABC9).

2.27.2. Executing ABC9_OPS pass (helper functions for ABC9).

2.27.3. Executing SCC pass (detecting logic loops).

Found 0 SCCs in module main.

Found 0 SCCs.

2.27.4. Executing ABC9_OPS pass (helper functions for ABC9).

2.27.5. Executing PROC pass (convert processes to netlists).

2.27.5.1. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.27.5.2. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

Removed a total of 0 dead cases.

2.27.5.3. Executing PROC_PRUNE pass (remove redundant assignments in processes).

Removed 0 redundant assignments.

Promoted 0 assignments to connections.

2.27.5.4. Executing PROC_INIT pass (extract init attributes).

2.27.5.5. Executing PROC_ARST pass (detect async resets in processes).

2.27.5.6. Executing PROC_ROM pass (convert switches to ROMs).

Converted 0 switches.

2.27.5.7. Executing PROC_MUX pass (convert decision trees to multiplexers).

2.27.5.8. Executing PROC_DLATCH pass (convert process syncs to latches).

2.27.5.9. Executing PROC_DFF pass (convert process syncs to FFs).

2.27.5.10. Executing PROC_MEMWR pass (convert process memory writes to cells).

2.27.5.11. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.27.5.12. Executing OPT_EXPR pass (perform const folding).

2.27.6. Executing TECHMAP pass (map to technology primitives).

2.27.6.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/techmap.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/techmap.v' to AST representation.

Generating RTLIL representation for module `\_90_simplemap_bool_ops'.

Generating RTLIL representation for module `\_90_simplemap_reduce_ops'.

Generating RTLIL representation for module `\_90_simplemap_logic_ops'.

Generating RTLIL representation for module `\_90_simplemap_compare_ops'.

Generating RTLIL representation for module `\_90_simplemap_various'.

Generating RTLIL representation for module `\_90_simplemap_registers'.

Generating RTLIL representation for module `\_90_shift_ops_shr_shl_sshl_sshr'.

Generating RTLIL representation for module `\_90_shift_shiftx'.

Generating RTLIL representation for module `\_90_fa'.

Generating RTLIL representation for module `\_90_lcu'.

Generating RTLIL representation for module `\_90_alu'.

Generating RTLIL representation for module `\_90_macc'.

Generating RTLIL representation for module `\_90_alumacc'.

Generating RTLIL representation for module `\$__div_mod_u'.

Generating RTLIL representation for module `\$__div_mod_trunc'.

Generating RTLIL representation for module `\_90_div'.

Generating RTLIL representation for module `\_90_mod'.

Generating RTLIL representation for module `\$__div_mod_floor'.

Generating RTLIL representation for module `\_90_divfloor'.

Generating RTLIL representation for module `\_90_modfloor'.

Generating RTLIL representation for module `\_90_pow'.

Generating RTLIL representation for module `\_90_pmux'.

Generating RTLIL representation for module `\_90_demux'.

Generating RTLIL representation for module `\_90_lut'.

Successfully finished Verilog frontend.

2.27.6.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~80 debug messages>

2.27.7. Executing OPT pass (performing simple optimizations).

2.27.7.1. Executing OPT_EXPR pass (perform const folding).

2.27.7.2. Executing OPT_MERGE pass (detect identical cells).

Removed a total of 0 cells.

2.27.7.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Removed 0 multiplexer ports.

2.27.7.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Performed a total of 0 changes.

2.27.7.5. Executing OPT_MERGE pass (detect identical cells).

Removed a total of 0 cells.

2.27.7.6. Executing OPT_DFF pass (perform DFF optimizations).

2.27.7.7. Executing OPT_CLEAN pass (remove unused cells and wires).

2.27.7.8. Executing OPT_EXPR pass (perform const folding).

2.27.7.9. Finished OPT passes. (There is nothing left to do.)

2.27.8. Executing TECHMAP pass (map to technology primitives).

2.27.8.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/abc9_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/abc9_map.v' to AST representation.

Successfully finished Verilog frontend.

2.27.8.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~2 debug messages>

2.27.9. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/abc9_model.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/abc9_model.v' to AST representation.

Generating RTLIL representation for module `$__ABC9_DELAY'.

Generating RTLIL representation for module `$__ABC9_SCC_BREAKER'.

Generating RTLIL representation for module `$__DFF_N__$abc9_flop'.

Generating RTLIL representation for module `$__DFF_P__$abc9_flop'.

Successfully finished Verilog frontend.

2.27.10. Executing ABC9_OPS pass (helper functions for ABC9).

2.27.11. Executing ABC9_OPS pass (helper functions for ABC9).

<suppressed ~2 debug messages>

2.27.12. Executing AIGMAP pass (map logic to AIG).

Module main: replaced 0 cells with 0 new cells, skipped 1 cells.

not replaced 1 cell types:

1 $_NOT_

2.27.12.1. Executing ABC9_OPS pass (helper functions for ABC9).

2.27.12.2. Executing XAIGER backend.

<suppressed ~5 debug messages>

Extracted 0 AND gates and 5 wires from module `main' to a netlist network with 1 inputs and 1 outputs.

2.27.12.3. Executing ABC9_EXE pass (technology mapping using ABC9).

2.27.12.4. Executing ABC9.

Running ABC command: "<yosys-exe-dir>/yosys-abc" -s -f <abc-temp-dir>/abc.script 2>&1

ABC: ABC command line: "source <abc-temp-dir>/abc.script".

ABC:

ABC: + read_lut <abc-temp-dir>/lutdefs.txt

ABC: + read_box <abc-temp-dir>/input.box

ABC: + &read <abc-temp-dir>/input.xaig

ABC: + &ps

ABC: <abc-temp-dir>/input : i/o = 1/ 1 and = 0 lev = 0 (0.00) mem = 0.00 MB box = 0 bb = 0

ABC: + &if -v

ABC: K = 4. Memory (bytes): Truth = 0. Cut = 48. Obj = 128. Set = 528. CutMin = no

ABC: Node = 0. Ch = 0. Total mem = 0.00 MB. Peak cut mem = 0.00 MB.

ABC: P: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: P: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: P: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: E: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: F: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: E: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: A: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: E: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: A: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: E: Del = 0.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: Total time = 0.00 sec

ABC: + &ps -l

ABC: <abc-temp-dir>/input : i/o = 1/ 1 and = 0 lev = 0 (0.00) mem = 0.00 MB box = 0 bb = 0

ABC: Mapping (K=0) : lut = 0 edge = 0 lev = 0 (0.00) mem = 0.00 MB

ABC: LUT = 0 : Ave = 0.00

ABC: + &write -n <abc-temp-dir>/output.aig

ABC: + time

ABC: elapse: 0.00 seconds, total: 0.00 seconds

2.27.12.5. Executing AIGER frontend.

<suppressed ~12 debug messages>

Removed 0 unused cells and 2 unused wires.

2.27.12.6. Executing ABC9_OPS pass (helper functions for ABC9).

ABC RESULTS: $lut cells: 1

ABC RESULTS: input signals: 1

ABC RESULTS: output signals: 1

Removing temp directory.

2.27.13. Executing TECHMAP pass (map to technology primitives).

2.27.13.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/abc9_unmap.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/abc9_unmap.v' to AST representation.

Generating RTLIL representation for module `\$__DFF_x__$abc9_flop'.

Generating RTLIL representation for module `\$__ABC9_SCC_BREAKER'.

Successfully finished Verilog frontend.

2.27.13.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~5 debug messages>

2.28. Executing TECHMAP pass (map to technology primitives).

2.28.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/microchip/cells_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/microchip/cells_map.v' to AST representation.

Generating RTLIL representation for module `\$_DFF_P_'.

Generating RTLIL representation for module `\$lut'.

Successfully finished Verilog frontend.

2.28.2. Continuing TECHMAP pass.

Using template $paramod\$lut\WIDTH=32'00000000000000000000000000000001\LUT=2'01 for cells of type $lut.

No more expansions possible.

<suppressed ~18 debug messages>

2.29. Executing OPT pass (performing simple optimizations).

2.29.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.29.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.29.3. Executing OPT_DFF pass (perform DFF optimizations).

2.29.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

Removed 0 unused cells and 4 unused wires.

<suppressed ~1 debug messages>

2.29.5. Finished fast OPT passes.

2.30. Executing SPLITNETS pass (splitting up multi-bit signals).

2.31. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

Removed 0 unused cells and 1 unused wires.

<suppressed ~1 debug messages>

2.32. Executing RMPORTS pass (remove ports with no connections).

Finding unconnected ports in module \main

Removed 0 unused ports.

Removing now-unused cell ports in module \main

2.33. Executing OPT pass (performing simple optimizations).

2.33.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module main.

2.33.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\main'.

Removed a total of 0 cells.

2.33.3. Executing OPT_DFF pass (perform DFF optimizations).

2.33.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \main..

2.33.5. Finished fast OPT passes.

2.34. Executing IOPADMAP pass (mapping inputs/outputs to IO-PAD cells).

Mapping port main.CLBIN0PPS_synchronized using IB.

Mapping port main.PPS_OUT1 using OB.

2.35. Executing SETUNDEF pass (replace undef values with defined constants).

2.36. Executing HIERARCHY pass (managing design hierarchy).

2.36.1. Analyzing design hierarchy..

Top module: \main

2.36.2. Analyzing design hierarchy..

Top module: \main

Removed 0 unused modules.

2.37. Printing statistics.

=== main ===

Number of wires: 4

Number of wire bits: 4

Number of public wires: 2

Number of public wire bits: 2

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 3

IB 1

LUT1 1

OB 1

2.38. Executing CHECK pass (checking for obvious problems).

Checking module main...

Found and reported 0 problems.

3. Executing SCC pass (detecting logic loops).

Found 0 SCCs in module main.

Found 0 SCCs.

4. Executing JSON backend.

End of script. Logfile hash: 602acaecb5, CPU: user 0.07s system 0.01s, MEM: 14.71 MB peak

Yosys 0.25 (git sha1 e02b7f64b, gcc 10.2.1-6 -fPIC -Os)

Time spent: 34% 1x abc9_exe (0 sec), 23% 12x read_verilog (0 sec), ...

Run place & route:

python -m fpga_interchange.yosys_json \

--schema_dir /usr/local/share/arch-defs/third_party/fpga-interchange-schema/interchange \

--device /usr/local/share/arch-defs/device/pic16f131xx_v1/fpga_interchange/chipdb.device \

synth.json out.netlist

python /usr/local/share/arch-defs/device/pic16f131xx_v1/fasm_generator.py --schema_dir /usr/local/share/arch-defs/third_party/fpga-interchange-schema/interchange /usr/local/share/arch-defs/device/pic16f131xx_v1/fpga_interchange/chipdb.device out.netlist out.phys out.fasm

build the output files:

python /usr/local/share/arch-defs/device/pic16f131xx_v1/bitstream/assembler.py -p ../input/project.json out.fasm bitstream.json

python /usr/local/share/arch-defs/device/pic16f131xx_v1/bitstream/format.py -t /usr/local/share/arch-defs/device/pic16f131xx_v1/templates/c_header_template.c bitstream.json ../bitstream.s

python /usr/local/share/arch-defs/result_generators/mapping_header.py -t /usr/local/share/arch-defs/device/pic16f131xx_v1/templates/output_mappings.h bitstream.json ../clb1_output_mappings.h

2. Executing SCC pass (detecting logic loops).

Found 0 SCCs in module main.

Found 0 SCCs.

3. Printing statistics.

=== main ===

Number of wires: 4

Number of wire bits: 4

Number of public wires: 2

Number of public wire bits: 2

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 3

IB 1

LUT1 1

OB 1

Draw the graphs:

Reading and parsing FASM file...

Reading XDC file...

Decoding...

Writing output file(s)...But very interesting is the out.fasm file. .fasm stands for FPGA Assembly; it’s a low-level file that describes the

FPGA layout before it’s converted into a bitstream.

# Created by the FPGA Interchange FASM Generator (v0.0.18)

BLE_X3Y3.BLE0.FLOPSEL.DISABLE

BLE_X3Y3.BLE0.LUT.INIT[15:0] = 16'b0101010101010101

CLKDIV[2:0] = 3'b001

MUX0.CLBIN[5:0] = 6'b000000

MUX0.INSYNC[2:0] = 3'b100

BLE_X3Y3.BLE0_LI0.IN0

PPS_X5Y3.OPAD0_O.LO_Y_2

This is very exciting, it has an exact detailed description of the configurations,

including the exact BLE LUT config, the settings of the clock divider, and it shows the BLE input 0 is connected to IN0

from our constraints file.

The PPS_X5Y3.OPAD0_O.LO_Y_2 line is a bit confusing; let’s ignore that for now.

The rest of the files are not too useful for our work.

Decoding the BLE LUT Configuration

Based on observing the requests, I was able to make a script that submits a zip file and unpacks the response.

As I was playing around I figured out that I can specify LUTs directly int he verilog in a compact form like this, where

16'hAAAA is the LUT config:

LUT4 #(.INIT(16'hAAAA)) name (

.I0(...),

.I1(...),

.I2(...),

.I3(...),

.O(...)

);

This makes reading and writing lots of LUT configurations really easy.

The Plan

My first thought was to make a single configuration where I filled up all the LUTs in the system, then I could just flip bits one at a time in the 16-bit LUT and find where the corresponding bit flipped in the bitstream, simple right?

The Reality

Note

If you want to actually run this yourself, you need to carefully manage the includes (main.xdc) to match the Verilog.

If it does not, it will refuse to run.

It turns out that if you try to make a logic design that comes even close to filling all LUTs, the synthesis engine just fails.

Based on the datasheet configuration (recall our data model?) each LUT input can connect to a subset of the signals.

The most useful ones are the CLBSWIN signals, a 32-bit wide input to the CLB block: CLBSWIN0-7 can connect to the A input,

CLBSWIN8-15 to B, CLBSWIN16-23 to C, and CLBSWIN24-31 to D. This means we can (try) to prevent the router from altering

our design by connecting the SW inputs to the corresponding LUT inputs in our design.

So we can make the following design:

LUT4 #(.INIT(16'hAAAA)) name (

.I0(CLBSWIN0),

.I1(CLBSWIN8),

.I2(CLBSWIN16),

.I3(CLBSWIN24),

.O(PPS_OUT1)

);

When we synthesize this it shows the expected results:

routed.svg

# Created by the FPGA Interchange FASM Generator (v0.0.18)

BLE_X3Y3.BLE0.FLOPSEL.DISABLE

BLE_X3Y3.BLE0.LUT.INIT[15:0] = 16'b1010101010101010

BLE_X3Y3.BLE0_LI0.CLBSWIN0

BLE_X3Y3.BLE0_LI1.CLBSWIN8

BLE_X3Y3.BLE0_LI2.CLBSWIN16

BLE_X3Y3.BLE0_LI3.CLBSWIN24

PPS_X5Y3.OPAD0_O.LO_Y_2

I tried to expand this by fanning out from the single output, layer by layer, with a random LUT configuration so it couldn’t be optimized out. (If a LUT configuration ignores an input signal, it will be optimized out).

Here is an example of a design that uses all 32 BLEs that can be implemented but fails to synthesize.

ble_fill_32.v

Note

Note: PPS 0 can actually be connected to BLE0\nI also use random LUT configs so they can’t be optimized out.

module main(

CLBSWIN0, CLBSWIN1, CLBSWIN2, CLBSWIN3, CLBSWIN4, CLBSWIN5, CLBSWIN6, CLBSWIN7,

CLBSWIN8, CLBSWIN9, CLBSWIN10, CLBSWIN11, CLBSWIN12, CLBSWIN13, CLBSWIN14, CLBSWIN15,

CLBSWIN16, CLBSWIN17, CLBSWIN18, CLBSWIN19, CLBSWIN20, CLBSWIN21, CLBSWIN22, CLBSWIN23,

CLBSWIN24, CLBSWIN25, CLBSWIN26, CLBSWIN27, CLBSWIN28, CLBSWIN29, CLBSWIN30, CLBSWIN31,

PPS_OUT0

);

input CLBSWIN0, CLBSWIN1, CLBSWIN2, CLBSWIN3, CLBSWIN4, CLBSWIN5, CLBSWIN6, CLBSWIN7;

input CLBSWIN8, CLBSWIN9, CLBSWIN10, CLBSWIN11, CLBSWIN12, CLBSWIN13, CLBSWIN14, CLBSWIN15;

input CLBSWIN16, CLBSWIN17, CLBSWIN18, CLBSWIN19, CLBSWIN20, CLBSWIN21, CLBSWIN22, CLBSWIN23;

input CLBSWIN24, CLBSWIN25, CLBSWIN26, CLBSWIN27, CLBSWIN28, CLBSWIN29, CLBSWIN30, CLBSWIN31;

output PPS_OUT0;

wire LUT4_0, LUT4_1, LUT4_2, LUT4_3, LUT4_4, LUT4_5, LUT4_6, LUT4_7, LUT4_8, LUT4_9;

wire LUT4_10, LUT4_11, LUT4_12, LUT4_13, LUT4_14, LUT4_15, LUT4_16, LUT4_17;

wire LUT4_18, LUT4_19, LUT4_20, LUT4_21, LUT4_22, LUT4_23, LUT4_24, LUT4_25;

wire LUT4_26, LUT4_27, LUT4_28, LUT4_29, LUT4_30, LUT4_31;

// First stage LUT connections

LUT4 #(.INIT(16'h2087)) lut0 (.I0(LUT4_1), .I1(LUT4_9), .I2(LUT4_17), .I3(LUT4_25), .O(LUT4_0));

assign PPS_OUT0 = LUT4_0;

// Second stage LUT connections

LUT4 #(.INIT(16'hf939)) lut1 (.I0(LUT4_2), .I1(LUT4_10), .I2(LUT4_18), .I3(LUT4_26), .O(LUT4_1));

LUT4 #(.INIT(16'hf7c2)) lut9 (.I0(LUT4_3), .I1(LUT4_11), .I2(LUT4_19), .I3(LUT4_27), .O(LUT4_9));

LUT4 #(.INIT(16'h944f)) lut17 (.I0(LUT4_4), .I1(LUT4_12), .I2(LUT4_20), .I3(LUT4_28), .O(LUT4_17));

LUT4 #(.INIT(16'h6f52)) lut25 (.I0(LUT4_5), .I1(LUT4_13), .I2(LUT4_21), .I3(LUT4_29), .O(LUT4_25));

// Third stage LUT connections

LUT4 #(.INIT(16'h68a2)) lut2 (.I0(LUT4_6), .I1(LUT4_14), .I2(LUT4_22), .I3(LUT4_30), .O(LUT4_2));

LUT4 #(.INIT(16'h2e34)) lut10 (.I0(LUT4_7), .I1(LUT4_15), .I2(LUT4_23), .I3(LUT4_31), .O(LUT4_10));

LUT4 #(.INIT(16'he58a)) lut18 (.I0(CLBSWIN24), .I1(LUT4_8), .I2(LUT4_16), .I3(LUT4_24), .O(LUT4_18));

// Leaf LUT connections

LUT4 #(.INIT(16'bb22)) lut3 (.I0(CLBSWIN0), .I1(CLBSWIN8), .I2(CLBSWIN16), .I3(CLBSWIN24), .O(LUT4_3));

LUT4 #(.INIT(16'h2718)) lut4 (.I0(CLBSWIN0), .I1(CLBSWIN8), .I2(CLBSWIN16), .I3(CLBSWIN24), .O(LUT4_4));

LUT4 #(.INIT(16'hdcf2)) lut5 (.I0(CLBSWIN0), .I1(CLBSWIN8), .I2(CLBSWIN16), .I3(CLBSWIN24), .O(LUT4_5));

LUT4 #(.INIT(16'hf4d6)) lut6 (.I0(CLBSWIN1), .I1(CLBSWIN9), .I2(CLBSWIN17), .I3(CLBSWIN25), .O(LUT4_6));

LUT4 #(.INIT(16'h83ff)) lut7 (.I0(CLBSWIN2), .I1(CLBSWIN10), .I2(CLBSWIN18), .I3(CLBSWIN26), .O(LUT4_7));

LUT4 #(.INIT(16'hebf8)) lut8 (.I0(CLBSWIN3), .I1(CLBSWIN11), .I2(CLBSWIN19), .I3(CLBSWIN27), .O(LUT4_8));

LUT4 #(.INIT(16'h05fa)) lut11 (.I0(CLBSWIN4), .I1(CLBSWIN12), .I2(CLBSWIN20), .I3(CLBSWIN28), .O(LUT4_11));

LUT4 #(.INIT(16'h8d2c)) lut12 (.I0(CLBSWIN5), .I1(CLBSWIN13), .I2(CLBSWIN21), .I3(CLBSWIN29), .O(LUT4_12));

LUT4 #(.INIT(16'h8c2f)) lut13 (.I0(CLBSWIN6), .I1(CLBSWIN14), .I2(CLBSWIN22), .I3(CLBSWIN30), .O(LUT4_13));

LUT4 #(.INIT(16'hd720)) lut14 (.I0(CLBSWIN7), .I1(CLBSWIN15), .I2(CLBSWIN23), .I3(CLBSWIN31), .O(LUT4_14));

LUT4 #(.INIT(16'ha9cf)) lut15 (.I0(CLBSWIN0), .I1(CLBSWIN8), .I2(CLBSWIN16), .I3(CLBSWIN24), .O(LUT4_15));

LUT4 #(.INIT(16'h8837)) lut16 (.I0(CLBSWIN1), .I1(CLBSWIN9), .I2(CLBSWIN17), .I3(CLBSWIN25), .O(LUT4_16));

LUT4 #(.INIT(16'hf3f9)) lut19 (.I0(CLBSWIN2), .I1(CLBSWIN10), .I2(CLBSWIN18), .I3(CLBSWIN26), .O(LUT4_19));

LUT4 #(.INIT(16'h3b19)) lut20 (.I0(CLBSWIN3), .I1(CLBSWIN11), .I2(CLBSWIN19), .I3(CLBSWIN27), .O(LUT4_20));

LUT4 #(.INIT(16'hc980)) lut21 (.I0(CLBSWIN4), .I1(CLBSWIN12), .I2(CLBSWIN20), .I3(CLBSWIN28), .O(LUT4_21));

LUT4 #(.INIT(16'h68f9)) lut22 (.I0(CLBSWIN5), .I1(CLBSWIN13), .I2(CLBSWIN21), .I3(CLBSWIN29), .O(LUT4_22));

LUT4 #(.INIT(16'h7367)) lut23 (.I0(CLBSWIN6), .I1(CLBSWIN14), .I2(CLBSWIN22), .I3(CLBSWIN30), .O(LUT4_23));

LUT4 #(.INIT(16'hc07f)) lut24 (.I0(CLBSWIN7), .I1(CLBSWIN15), .I2(CLBSWIN23), .I3(CLBSWIN31), .O(LUT4_24));

LUT4 #(.INIT(16'hd4ec)) lut26 (.I0(CLBSWIN0), .I1(CLBSWIN8), .I2(CLBSWIN16), .I3(CLBSWIN24), .O(LUT4_26));

LUT4 #(.INIT(16'h9f5e)) lut27 (.I0(CLBSWIN1), .I1(CLBSWIN9), .I2(CLBSWIN17), .I3(CLBSWIN25), .O(LUT4_27));

LUT4 #(.INIT(16'hc319)) lut28 (.I0(CLBSWIN2), .I1(CLBSWIN10), .I2(CLBSWIN18), .I3(CLBSWIN26), .O(LUT4_28));

LUT4 #(.INIT(16'hab98)) lut29 (.I0(CLBSWIN3), .I1(CLBSWIN11), .I2(CLBSWIN19), .I3(CLBSWIN27), .O(LUT4_29));

LUT4 #(.INIT(16'hff75)) lut30 (.I0(CLBSWIN4), .I1(CLBSWIN12), .I2(CLBSWIN20), .I3(CLBSWIN28), .O(LUT4_30));

LUT4 #(.INIT(16'h2ac5)) lut31 (.I0(CLBSWIN5), .I1(CLBSWIN13), .I2(CLBSWIN21), .I3(CLBSWIN29), .O(LUT4_31));

endmoduleThe best I could do was 23 LUTs in a single design:

ble_fill_23.v

(* CLKDIV = 3'd0 *)

module lut5group #(

// One 80-bit parameter: 5 * 16-bit LUT tables (5*4 nibbles = 20 nibbles)

parameter [79:0] LUTS_INIT = 80'h00000000000000000000

)(

// Single 16-bit input, where bits are grouped as:

// in[3:0] -> Group 1 (for LUT1)

// in[7:4] -> Group 2 (for LUT2)

// in[11:8] -> Group 3 (for LUT3)

// in[15:12] -> Group 4 (for LUT4)

input [15:0] in,

output out

);

// Slice the 80-bit LUTS_INIT into five 16-bit LUT INIT values.

localparam [15:0] LUT1_INIT = LUTS_INIT[15:0];

localparam [15:0] LUT2_INIT = LUTS_INIT[31:16];

localparam [15:0] LUT3_INIT = LUTS_INIT[47:32];

localparam [15:0] LUT4_INIT = LUTS_INIT[63:48];

localparam [15:0] LUT5_INIT = LUTS_INIT[79:64];

// Wires for outputs of the first-stage LUTs.

wire group1_out, group2_out, group3_out, group4_out;

// First-stage LUTs: each processes one group of 4 input bits.

LUT4 #(.INIT(LUT1_INIT)) lut1 (

.I0(in[0]),

.I1(in[1]),

.I2(in[2]),

.I3(in[3]),

.O(group1_out)

);

LUT4 #(.INIT(LUT2_INIT)) lut2 (

.I0(in[4]),

.I1(in[5]),

.I2(in[6]),

.I3(in[7]),

.O(group2_out)

);

LUT4 #(.INIT(LUT3_INIT)) lut3 (

.I0(in[8]),

.I1(in[9]),

.I2(in[10]),

.I3(in[11]),

.O(group3_out)

);

LUT4 #(.INIT(LUT4_INIT)) lut4 (

.I0(in[12]),

.I1(in[13]),

.I2(in[14]),

.I3(in[15]),

.O(group4_out)

);

// Second-stage LUT: combines the four group outputs.

LUT4 #(.INIT(LUT5_INIT)) lut5 (

.I0(group1_out),

.I1(group2_out),

.I2(group3_out),

.I3(group4_out),

.O(out)

);

endmodule

module main (

// 16 switch inputs

input CLBSWIN0, CLBSWIN8, CLBSWIN16, CLBSWIN24,

input CLBSWIN1, CLBSWIN9, CLBSWIN17, CLBSWIN25,

input CLBSWIN2, CLBSWIN10, CLBSWIN18, CLBSWIN26,

input CLBSWIN3, CLBSWIN11, CLBSWIN19, CLBSWIN27,

// Four outputs

output PPS_OUT0,

output PPS_OUT1,

output PPS_OUT2,

output PPS_OUT3,

output PPS_OUT4,

output PPS_OUT5,

);

// Combine the 16 individual inputs into one 16-bit signal.

wire [15:0] my_inputs = {

CLBSWIN27, CLBSWIN19, CLBSWIN11, CLBSWIN3,

CLBSWIN26, CLBSWIN18, CLBSWIN10, CLBSWIN2,

CLBSWIN25, CLBSWIN17, CLBSWIN9, CLBSWIN1,

CLBSWIN24, CLBSWIN16, CLBSWIN8, CLBSWIN0

};

// Instantiate the first LUT grouping module using a single 80-bit literal.

// The 80-bit value encodes five 16-bit LUT INIT values.

// Bits [15:0] -> LUT1_INIT, [31:16] -> LUT2_INIT,

// Bits [47:32] -> LUT3_INIT, [63:48] -> LUT4_INIT,

// Bits [79:64] -> LUT5_INIT.

lut5group #(

.LUTS_INIT(80'hf6074086bd89639debf4)

) my_lut_group (

.in(my_inputs),

.out(PPS_OUT0)

);

// Instantiate the second LUT grouping module.

lut5group #(

.LUTS_INIT(80'he698a9fb27e04f49ffda)

) my_lut_group2 (

.in(my_inputs),

.out(PPS_OUT1)

);

// Instantiate the third LUT grouping module.

lut5group #(

.LUTS_INIT(80'hfb8a1ade450a1e5c9408)

) my_lut_group3 (

.in(my_inputs),

.out(PPS_OUT2)

);

LUT4 #(.INIT(16'hf607)) lut1 (

.I0(my_inputs[4]),

.I1(my_inputs[5]),

.I2(my_inputs[6]),

.I3(my_inputs[7]),

.O(PPS_OUT3)

);

LUT4 #(.INIT(16'h8821)) lut2 (

.I0(my_inputs[0]),

.I1(my_inputs[1]),

.I2(my_inputs[2]),

.I3(my_inputs[3]),

.O(PPS_OUT4)

);

endmoduleIdentifying BLE LUT Locations

But once I have this file I can submit it to make the base configuration, and then generate variants where I flip one bit in the LUT config, then look for a corresponding bit in the bitstream output.

After we submit all the variants we now need to process the results. I want to process the fasm file because

it has an exact description of the hardware, but it looks like this:

BLE_X1Y2.BLE0.LUT.INIT[15:0] = 16'b1110101111110100

BLE_X1Y3.BLE0.LUT.INIT[15:0] = 16'b1111111100000000

BLE_X1Y4.BLE0.LUT.INIT[15:0] = 16'b1001010000001000

BLE_X1Y6.BLE0.LUT.INIT[15:0] = 16'b0001111001011100

BLE_X1Y7.BLE0.LUT.INIT[15:0] = 1111000001100111

BLE_X1Y8.BLE0.LUT.INIT[15:0] = 1010101010101010

BLE_X1Y9.BLE0.LUT.INIT[15:0] = 1111111100000000

BLE_X2Y3.BLE0.LUT.INIT[15:0] = 0001101011011110

BLE_X2Y4.BLE0.LUT.INIT[15:0] = 0110001110011101

BLE_X2Y6.BLE0.LUT.INIT[15:0] = 0100111101001001

BLE_X2Y8.BLE0.LUT.INIT[15:0] = 0100000010000110

BLE_X2Y9.BLE0.LUT.INIT[15:0] = 1111111111011010

BLE_X3Y3.BLE0.LUT.INIT[15:0] = 1111011000000111

BLE_X3Y5.BLE0.LUT.INIT[15:0] = 1111000011110000

BLE_X3Y7.BLE0.LUT.INIT[15:0] = 1111111100000000

BLE_X3Y8.BLE0.LUT.INIT[15:0] = 1011110110001001

BLE_X3Y9.BLE0.LUT.INIT[15:0] = 1000100000100001

BLE_X4Y3.BLE0.LUT.INIT[15:0] = 1010100111111011

BLE_X4Y4.BLE0.LUT.INIT[15:0] = 0100010100001010

BLE_X4Y5.BLE0.LUT.INIT[15:0] = 0010011111100000

BLE_X4Y7.BLE0.LUT.INIT[15:0] = 1101101010100100

BLE_X4Y8.BLE0.LUT.INIT[15:0] = 1111101110001010

BLE_X4Y9.BLE0.LUT.INIT[15:0] = 1100110011001100

We need to map the BLE_X3Y3 etc. to the BLE number, luckely we have the routed.svg:

routed.svg

If you squint long and hard enough you will realize the BLEs are arranged in rows of 4:

| Y | X=1 | X=2 | X=3 | X=4 |

|---|---|---|---|---|

| 1 | ||||

| 2 | BLE0 | BLE1 | BLE2 | BLE3 |

| 3 | BLE4 | BLE5 | BLE6 | BLE7 |

| 4 | BLE8 | BLE9 | BLE10 | BLE11 |

| 5 | BLE12 | BLE13 | BLE14 | BLE15 |

| 6 | BLE16 | BLE17 | BLE18 | BLE19 |

| 7 | BLE20 | BLE21 | BLE22 | BLE23 |

| 8 | BLE24 | BLE25 | BLE26 | BLE27 |

| 9 | BLE28 | BLE29 | BLE30 | BLE31 |

We can add this to our data model:

class BLEXY(Enum):

BLE_X1Y2 = 0

...

BLE_X4Y9 = 31

Full BLE Location Data Model

The names exactly match the fasm to ease parsing.

class BLEXY(Enum):

BLE_X1Y2 = 0

BLE_X2Y2 = 1

BLE_X3Y2 = 2

BLE_X4Y2 = 3

BLE_X1Y3 = 4

BLE_X2Y3 = 5

BLE_X3Y3 = 6

BLE_X4Y3 = 7

BLE_X1Y4 = 8

BLE_X2Y4 = 9

BLE_X3Y4 = 10

BLE_X4Y4 = 11

BLE_X1Y5 = 12

BLE_X2Y5 = 13

BLE_X3Y5 = 14

BLE_X4Y5 = 15

BLE_X1Y6 = 16

BLE_X2Y6 = 17

BLE_X3Y6 = 18

BLE_X4Y6 = 19

BLE_X1Y7 = 20

BLE_X2Y7 = 21

BLE_X3Y7 = 22

BLE_X4Y7 = 23

BLE_X1Y8 = 24

BLE_X2Y8 = 25

BLE_X3Y8 = 26

BLE_X4Y8 = 27

BLE_X1Y9 = 28

BLE_X2Y9 = 29

BLE_X3Y9 = 30

BLE_X4Y9 = 31We can now make our first pass FASM parsing class for the BLE FLOPSEL and LUT lines

example fasm lines:

BLE_X1Y2.BLE0.FLOPSEL.DISABLE

BLE_X1Y2.BLE0.LUT.INIT[15:0] = 16'b1110101111110100

class FASM:

def __init__(self, fasm_file: Path):

self.LUTS = defaultdict(BLE_CFG)

with open(fasm_file, "r") as f:

for l in f.readlines():

if l.startswith("#"):

continue

if l.startswith("BLE_X"):

self.parse_ble(l)

continue

print(f"Unhandled line: {repr(l)}")

def parse_ble(self, line):

parts = line.split(".")

try:

ble_sel = BLEXY.__members__[parts[0]]

if parts[1] == "BLE0":

if parts[2] == "FLOPSEL":

# ex: BLE_X1Y2.BLE0.FLOPSEL.DISABLE

self.LUTS[ble_sel].FLOPSEL = FLOPSEL.__members__[parts[3].strip()]

return

if parts[2] == "LUT":

# ex: BLE_X1Y2.BLE0.LUT.INIT[15:0] = 16'b1110101111110100

self.LUTS[ble_sel].LUT_CONFIG = parts[-1][-17:-1]

return

except Exception as e:

raise RuntimeError(f"Error parsing line '{line}'") from e

print(f"Unhandled ble line: {parts}")

return

After parsing both the generated bitstreams and the FASM files we can visualize the result below, it’s sparse because

we only obtained data for 28 more or less random LUTs in the output. Below, I annotate them in the format <BLE #>:<LUT Bit>. Luckily, we got

BLE 0 and BLE 31 so we know the bounds. If you look long enough you will see there is a pattern repeating every 8 words

(I added a bold line to help you see it).

28 BLE LUT Bit Map

| Word | +0 | +1 | +2 | +3 | +4 | +5 | +6 | +7 | +8 | +9 | +10 | +11 | +12 | +13 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | ||||||||||||||

| 1 | ||||||||||||||

| 2 | ||||||||||||||

| 3 | ||||||||||||||

| 4 | ||||||||||||||

| 5 | ||||||||||||||

| 6 | ||||||||||||||

| 7 | ||||||||||||||

| 8 | ||||||||||||||

| 9 | ||||||||||||||

| 10 | ||||||||||||||

| 11 | ||||||||||||||

| 12 | ||||||||||||||

| 13 | ||||||||||||||

| 14 | ||||||||||||||

| 15 | ||||||||||||||

| 16 | ||||||||||||||

| 17 | 31:12 | 31:13 | 31:14 | 31:15 | 31:8 | 31:9 | 31:10 | 31:11 | ||||||

| 18 | 31:4 | 31:5 | 31:6 | 31:7 | ||||||||||

| 19 | 31:0 | 31:1 | 31:2 | 31:3 | 30:12 | 30:13 | 30:14 | 30:15 | ||||||

| 20 | 30:8 | 30:9 | 30:10 | 30:11 | ||||||||||

| 21 | 30:4 | 30:5 | 30:6 | 30:7 | 30:0 | 30:1 | 30:2 | 30:3 | ||||||

| 22 | 29:12 | 29:13 | 29:14 | 29:15 | ||||||||||

| 23 | 29:8 | 29:9 | 29:10 | 29:11 | 29:4 | 29:5 | 29:6 | 29:7 | ||||||

| 24 | 29:0 | 29:1 | 29:2 | 29:3 | ||||||||||

| 25 | 28:12 | 28:13 | 28:14 | 28:15 | 28:8 | 28:9 | 28:10 | 28:11 | ||||||

| 26 | 28:4 | 28:5 | 28:6 | 28:7 | ||||||||||

| 27 | 28:0 | 28:1 | 28:2 | 28:3 | 27:12 | 27:13 | 27:14 | 27:15 | ||||||

| 28 | 27:8 | 27:9 | 27:10 | 27:11 | ||||||||||

| 29 | 27:4 | 27:5 | 27:6 | 27:7 | 27:0 | 27:1 | 27:2 | 27:3 | ||||||

| 30 | 26:12 | 26:13 | 26:14 | 26:15 | ||||||||||

| 31 | 26:8 | 26:9 | 26:10 | 26:11 | 26:4 | 26:5 | 26:6 | 26:7 | ||||||

| 32 | 26:0 | 26:1 | 26:2 | 26:3 | ||||||||||

| 33 | 25:12 | 25:13 | 25:14 | 25:15 | 25:8 | 25:9 | 25:10 | 25:11 | ||||||

| 34 | 25:4 | 25:5 | 25:6 | 25:7 | ||||||||||

| 35 | 25:0 | 25:1 | 25:2 | 25:3 | 24:12 | 24:13 | 24:14 | 24:15 | ||||||

| 36 | 24:8 | 24:9 | 24:10 | 24:11 | ||||||||||

| 37 | 24:4 | 24:5 | 24:6 | 24:7 | 24:0 | 24:1 | 24:2 | 24:3 | ||||||

| 38 | 23:12 | 23:13 | 23:14 | 23:15 | ||||||||||

| 39 | 23:8 | 23:9 | 23:10 | 23:11 | 23:4 | 23:5 | 23:6 | 23:7 | ||||||

| 40 | 23:0 | 23:1 | 23:2 | 23:3 | ||||||||||

| 41 | 22:12 | 22:13 | 22:14 | 22:15 | 22:8 | 22:9 | 22:10 | 22:11 | ||||||

| 42 | 22:4 | 22:5 | 22:6 | 22:7 | ||||||||||

| 43 | 22:0 | 22:1 | 22:2 | 22:3 | ||||||||||

| 44 | ||||||||||||||

| 45 | ||||||||||||||

| 46 | 20:12 | 20:13 | 20:14 | 20:15 | ||||||||||

| 47 | 20:8 | 20:9 | 20:10 | 20:11 | 20:4 | 20:5 | 20:6 | 20:7 | ||||||

| 48 | 20:0 | 20:1 | 20:2 | 20:3 | ||||||||||

| 49 | ||||||||||||||

| 50 | ||||||||||||||

| 51 | ||||||||||||||

| 52 | ||||||||||||||

| 53 | ||||||||||||||

| 54 | 17:12 | 17:13 | 17:14 | 17:15 | ||||||||||

| 55 | 17:8 | 17:9 | 17:10 | 17:11 | 17:4 | 17:5 | 17:6 | 17:7 | ||||||

| 56 | 17:0 | 17:1 | 17:2 | 17:3 | ||||||||||

| 57 | 16:12 | 16:13 | 16:14 | 16:15 | 16:8 | 16:9 | 16:10 | 16:11 | ||||||

| 58 | 16:4 | 16:5 | 16:6 | 16:7 | ||||||||||

| 59 | 16:0 | 16:1 | 16:2 | 16:3 | 15:12 | 15:13 | 15:14 | 15:15 | ||||||

| 60 | 15:8 | 15:9 | 15:10 | 15:11 | ||||||||||

| 61 | 15:4 | 15:5 | 15:6 | 15:7 | 15:0 | 15:1 | 15:2 | 15:3 | ||||||

| 62 | 14:12 | 14:13 | 14:14 | 14:15 | ||||||||||

| 63 | 14:8 | 14:9 | 14:10 | 14:11 | 14:4 | 14:5 | 14:6 | 14:7 | ||||||

| 64 | 14:0 | 14:1 | 14:2 | 14:3 | ||||||||||

| 65 | ||||||||||||||

| 66 | ||||||||||||||

| 67 | ||||||||||||||

| 68 | ||||||||||||||

| 69 | ||||||||||||||

| 70 | 11:12 | 11:13 | 11:14 | 11:15 | ||||||||||

| 71 | 11:8 | 11:9 | 11:10 | 11:11 | 11:4 | 11:5 | 11:6 | 11:7 | ||||||

| 72 | 11:0 | 11:1 | 11:2 | 11:3 | ||||||||||

| 73 | ||||||||||||||

| 74 | ||||||||||||||

| 75 | 9:12 | 9:13 | 9:14 | 9:15 | ||||||||||

| 76 | 9:8 | 9:9 | 9:10 | 9:11 | ||||||||||

| 77 | 9:4 | 9:5 | 9:6 | 9:7 | 9:0 | 9:1 | 9:2 | 9:3 | ||||||

| 78 | 8:12 | 8:13 | 8:14 | 8:15 | ||||||||||

| 79 | 8:8 | 8:9 | 8:10 | 8:11 | 8:4 | 8:5 | 8:6 | 8:7 | ||||||

| 80 | 8:0 | 8:1 | 8:2 | 8:3 | ||||||||||

| 81 | 7:12 | 7:13 | 7:14 | 7:15 | 7:8 | 7:9 | 7:10 | 7:11 | ||||||

| 82 | 7:4 | 7:5 | 7:6 | 7:7 | ||||||||||

| 83 | 7:0 | 7:1 | 7:2 | 7:3 | 6:12 | 6:13 | 6:14 | 6:15 | ||||||

| 84 | 6:8 | 6:9 | 6:10 | 6:11 | ||||||||||

| 85 | 6:4 | 6:5 | 6:6 | 6:7 | 6:0 | 6:1 | 6:2 | 6:3 | ||||||

| 86 | 5:12 | 5:13 | 5:14 | 5:15 | ||||||||||

| 87 | 5:8 | 5:9 | 5:10 | 5:11 | 5:4 | 5:5 | 5:6 | 5:7 | ||||||

| 88 | 5:0 | 5:1 | 5:2 | 5:3 | ||||||||||

| 89 | 4:12 | 4:13 | 4:14 | 4:15 | 4:8 | 4:9 | 4:10 | 4:11 | ||||||

| 90 | 4:4 | 4:5 | 4:6 | 4:7 | ||||||||||

| 91 | 4:0 | 4:1 | 4:2 | 4:3 | ||||||||||

| 92 | ||||||||||||||

| 93 | ||||||||||||||

| 94 | ||||||||||||||

| 95 | ||||||||||||||

| 96 | ||||||||||||||

| 97 | ||||||||||||||

| 98 | ||||||||||||||

| 99 | 0:12 | 0:13 | 0:14 | 0:15 | ||||||||||

| 100 | 0:8 | 0:9 | 0:10 | 0:11 | ||||||||||

| 101 | 0:4 | 0:5 | 0:6 | 0:7 | 0:0 | 0:1 | 0:2 | 0:3 |

We can use that to extrapolate the LUT locations for every BLE:

| Word | +0 | +1 | +2 | +3 | +4 | +5 | +6 | +7 | +8 | +9 | +10 | +11 | +12 | +13 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | ||||||||||||||

| 1 | ||||||||||||||

| 2 | ||||||||||||||

| 3 | ||||||||||||||

| 4 | ||||||||||||||

| 5 | ||||||||||||||

| 6 | ||||||||||||||

| 7 | ||||||||||||||

| 8 | ||||||||||||||

| 9 | ||||||||||||||

| 10 | ||||||||||||||

| 11 | ||||||||||||||

| 12 | ||||||||||||||

| 13 | ||||||||||||||

| 14 | ||||||||||||||

| 15 | ||||||||||||||

| 16 | ||||||||||||||

| 17 | 31:12 | 31:13 | 31:14 | 31:15 | 31:8 | 31:9 | 31:10 | 31:11 | ||||||

| 18 | 31:4 | 31:5 | 31:6 | 31:7 | ||||||||||

| 19 | 31:0 | 31:1 | 31:2 | 31:3 | 30:12 | 30:13 | 30:14 | 30:15 | ||||||

| 20 | 30:8 | 30:9 | 30:10 | 30:11 | ||||||||||

| 21 | 30:4 | 30:5 | 30:6 | 30:7 | 30:0 | 30:1 | 30:2 | 30:3 | ||||||

| 22 | 29:12 | 29:13 | 29:14 | 29:15 | ||||||||||

| 23 | 29:8 | 29:9 | 29:10 | 29:11 | 29:4 | 29:5 | 29:6 | 29:7 | ||||||

| 24 | 29:0 | 29:1 | 29:2 | 29:3 | ||||||||||

| 25 | 28:12 | 28:13 | 28:14 | 28:15 | 28:8 | 28:9 | 28:10 | 28:11 | ||||||

| 26 | 28:4 | 28:5 | 28:6 | 28:7 | ||||||||||

| 27 | 28:0 | 28:1 | 28:2 | 28:3 | 27:12 | 27:13 | 27:14 | 27:15 | ||||||

| 28 | 27:8 | 27:9 | 27:10 | 27:11 | ||||||||||

| 29 | 27:4 | 27:5 | 27:6 | 27:7 | 27:0 | 27:1 | 27:2 | 27:3 | ||||||

| 30 | 26:12 | 26:13 | 26:14 | 26:15 | ||||||||||

| 31 | 26:8 | 26:9 | 26:10 | 26:11 | 26:4 | 26:5 | 26:6 | 26:7 | ||||||

| 32 | 26:0 | 26:1 | 26:2 | 26:3 | ||||||||||

| 33 | 25:12 | 25:13 | 25:14 | 25:15 | 25:8 | 25:9 | 25:10 | 25:11 | ||||||

| 34 | 25:4 | 25:5 | 25:6 | 25:7 | ||||||||||

| 35 | 25:0 | 25:1 | 25:2 | 25:3 | 24:12 | 24:13 | 24:14 | 24:15 | ||||||

| 36 | 24:8 | 24:9 | 24:10 | 24:11 | ||||||||||

| 37 | 24:4 | 24:5 | 24:6 | 24:7 | 24:0 | 24:1 | 24:2 | 24:3 | ||||||

| 38 | 23:12 | 23:13 | 23:14 | 23:15 | ||||||||||

| 39 | 23:8 | 23:9 | 23:10 | 23:11 | 23:4 | 23:5 | 23:6 | 23:7 | ||||||

| 40 | 23:0 | 23:1 | 23:2 | 23:3 | ||||||||||

| 41 | 22:12 | 22:13 | 22:14 | 22:15 | 22:8 | 22:9 | 22:10 | 22:11 | ||||||

| 42 | 22:4 | 22:5 | 22:6 | 22:7 | ||||||||||

| 43 | 22:0 | 22:1 | 22:2 | 22:3 | 21:12 | 21:13 | 21:14 | 21:15 | ||||||

| 44 | 21:8 | 21:9 | 21:10 | 21:11 | ||||||||||

| 45 | 21:4 | 21:5 | 21:6 | 21:7 | 21:0 | 21:1 | 21:2 | 21:3 | ||||||

| 46 | 20:12 | 20:13 | 20:14 | 20:15 | ||||||||||

| 47 | 20:8 | 20:9 | 20:10 | 20:11 | 20:4 | 20:5 | 20:6 | 20:7 | ||||||

| 48 | 20:0 | 20:1 | 20:2 | 20:3 | ||||||||||

| 49 | 19:12 | 19:13 | 19:14 | 19:15 | 19:8 | 19:9 | 19:10 | 19:11 | ||||||

| 50 | 19:4 | 19:5 | 19:6 | 19:7 | ||||||||||

| 51 | 19:0 | 19:1 | 19:2 | 19:3 | 18:12 | 18:13 | 18:14 | 18:15 | ||||||

| 52 | 18:8 | 18:9 | 18:10 | 18:11 | ||||||||||

| 53 | 18:4 | 18:5 | 18:6 | 18:7 | 18:0 | 18:1 | 18:2 | 18:3 | ||||||

| 54 | 17:12 | 17:13 | 17:14 | 17:15 | ||||||||||

| 55 | 17:8 | 17:9 | 17:10 | 17:11 | 17:4 | 17:5 | 17:6 | 17:7 | ||||||

| 56 | 17:0 | 17:1 | 17:2 | 17:3 | ||||||||||

| 57 | 16:12 | 16:13 | 16:14 | 16:15 | 16:8 | 16:9 | 16:10 | 16:11 | ||||||

| 58 | 16:4 | 16:5 | 16:6 | 16:7 | ||||||||||

| 59 | 16:0 | 16:1 | 16:2 | 16:3 | 15:12 | 15:13 | 15:14 | 15:15 | ||||||

| 60 | 15:8 | 15:9 | 15:10 | 15:11 | ||||||||||

| 61 | 15:4 | 15:5 | 15:6 | 15:7 | 15:0 | 15:1 | 15:2 | 15:3 | ||||||

| 62 | 14:12 | 14:13 | 14:14 | 14:15 | ||||||||||

| 63 | 14:8 | 14:9 | 14:10 | 14:11 | 14:4 | 14:5 | 14:6 | 14:7 | ||||||

| 64 | 14:0 | 14:1 | 14:2 | 14:3 | ||||||||||

| 65 | 13:12 | 13:13 | 13:14 | 13:15 | 13:8 | 13:9 | 13:10 | 13:11 | ||||||

| 66 | 13:4 | 13:5 | 13:6 | 13:7 | ||||||||||

| 67 | 13:0 | 13:1 | 13:2 | 13:3 | 12:12 | 12:13 | 12:14 | 12:15 | ||||||

| 68 | 12:8 | 12:9 | 12:10 | 12:11 | ||||||||||

| 69 | 12:4 | 12:5 | 12:6 | 12:7 | 12:0 | 12:1 | 12:2 | 12:3 | ||||||

| 70 | 11:12 | 11:13 | 11:14 | 11:15 | ||||||||||

| 71 | 11:8 | 11:9 | 11:10 | 11:11 | 11:4 | 11:5 | 11:6 | 11:7 | ||||||

| 72 | 11:0 | 11:1 | 11:2 | 11:3 | ||||||||||

| 73 | 10:12 | 10:13 | 10:14 | 10:15 | 10:8 | 10:9 | 10:10 | 10:11 | ||||||

| 74 | 10:4 | 10:5 | 10:6 | 10:7 | ||||||||||

| 75 | 10:0 | 10:1 | 10:2 | 10:3 | 9:12 | 9:13 | 9:14 | 9:15 | ||||||

| 76 | 9:8 | 9:9 | 9:10 | 9:11 | ||||||||||

| 77 | 9:4 | 9:5 | 9:6 | 9:7 | 9:0 | 9:1 | 9:2 | 9:3 | ||||||

| 78 | 8:12 | 8:13 | 8:14 | 8:15 | ||||||||||

| 79 | 8:8 | 8:9 | 8:10 | 8:11 | 8:4 | 8:5 | 8:6 | 8:7 | ||||||

| 80 | 8:0 | 8:1 | 8:2 | 8:3 | ||||||||||

| 81 | 7:12 | 7:13 | 7:14 | 7:15 | 7:8 | 7:9 | 7:10 | 7:11 | ||||||

| 82 | 7:4 | 7:5 | 7:6 | 7:7 | ||||||||||

| 83 | 7:0 | 7:1 | 7:2 | 7:3 | 6:12 | 6:13 | 6:14 | 6:15 | ||||||

| 84 | 6:8 | 6:9 | 6:10 | 6:11 | ||||||||||

| 85 | 6:4 | 6:5 | 6:6 | 6:7 | 6:0 | 6:1 | 6:2 | 6:3 | ||||||

| 86 | 5:12 | 5:13 | 5:14 | 5:15 | ||||||||||

| 87 | 5:8 | 5:9 | 5:10 | 5:11 | 5:4 | 5:5 | 5:6 | 5:7 | ||||||

| 88 | 5:0 | 5:1 | 5:2 | 5:3 | ||||||||||

| 89 | 4:12 | 4:13 | 4:14 | 4:15 | 4:8 | 4:9 | 4:10 | 4:11 | ||||||

| 90 | 4:4 | 4:5 | 4:6 | 4:7 | ||||||||||

| 91 | 4:0 | 4:1 | 4:2 | 4:3 | 3:12 | 3:13 | 3:14 | 3:15 | ||||||

| 92 | 3:8 | 3:9 | 3:10 | 3:11 | ||||||||||

| 93 | 3:4 | 3:5 | 3:6 | 3:7 | 3:0 | 3:1 | 3:2 | 3:3 | ||||||

| 94 | 2:12 | 2:13 | 2:14 | 2:15 | ||||||||||

| 95 | 2:8 | 2:9 | 2:10 | 2:11 | 2:4 | 2:5 | 2:6 | 2:7 | ||||||

| 96 | 2:0 | 2:1 | 2:2 | 2:3 | ||||||||||

| 97 | 1:12 | 1:13 | 1:14 | 1:15 | 1:8 | 1:9 | 1:10 | 1:11 | ||||||

| 98 | 1:4 | 1:5 | 1:6 | 1:7 | ||||||||||

| 99 | 1:0 | 1:1 | 1:2 | 1:3 | 0:12 | 0:13 | 0:14 | 0:15 | ||||||

| 100 | 0:8 | 0:9 | 0:10 | 0:11 | ||||||||||

| 101 | 0:4 | 0:5 | 0:6 | 0:7 | 0:0 | 0:1 | 0:2 | 0:3 |

Decoding the BLE LUT Input Configuration

Next we need to decode what bits in the BLE configuration correspond to the input settings. To do this we need to change the inputs for a LUT without the rest of the design changing, this is much more challenging.

The first thing to notice is that if we look at the settings for the LUT input register, we see that the SW setting bits cover the whole bit width of the input register (i.e., the most significant bit (MSB) isn’t fixed but varies with the SWIN selection). So, if we iterate through the CLBSWIN values we can cover all the bit changes.

class LUT_IN_A(IntEnum):

"""BLE INPUT A[4:0]"""

# ...

CLBSWIN0 = 0b01100

CLBSWIN1 = 0b01101

CLBSWIN2 = 0b01110

CLBSWIN3 = 0b01111

CLBSWIN4 = 0b10000

CLBSWIN5 = 0b10001

CLBSWIN6 = 0b10010

CLBSWIN7 = 0b10011

# ...

Generating Variants

We can iterate on this simple base design cycling the inputs through the SWIN values (generating all 32 variants).

module main (

input CLBSWIN0, CLBSWIN8, CLBSWIN16, CLBSWIN24,

output BLE_OUT

);

LUT4 #(.INIT(16'hABCD)) ble (

.I0(CLBSWIN0),

.I1(CLBSWIN8),

.I2(CLBSWIN16),

.I3(CLBSWIN24),

.O(BLE_OUT)

);

endmodule

Iter SWIN Vals

import shutil, tempfile

from pathlib import Path

from request_func import submit_and_extract

base_dir = Path("blog_single_lut_in_iter")

out_dir = Path("blog_single_lut_in_iter_out")

out_dir.mkdir(exist_ok=True)

# Submit base configuration

with tempfile.TemporaryDirectory() as tdir:

proj = Path(tdir) / "project"

shutil.copytree(base_dir, proj)

print("Submitting base configuration")

res = submit_and_extract(proj, out_dir)

print("Output at", res.output_dir.resolve())

# Base mapping: I0->CLBSWIN0, I1->CLBSWIN8, I2->CLBSWIN16, I3->CLBSWIN24.

base_ports = {0: "CLBSWIN0", 1: "CLBSWIN8", 2: "CLBSWIN16", 3: "CLBSWIN24"}

port_ranges = {0: range(0, 8), 1: range(8, 16), 2: range(16, 24), 3: range(24, 32)}

for i, rng in port_ranges.items():

for num in rng:

new_port = f"CLBSWIN{num}"

if new_port == base_ports[i]:

continue

with tempfile.TemporaryDirectory() as tdir:

proj = Path(tdir) / "project"

shutil.copytree(base_dir, proj)

for fname in ["main.v", "main.xdc"]:

content = (proj / fname).read_text(encoding="utf-8")

(proj / fname).write_text(content.replace(base_ports[i], new_port), encoding="utf-8")

print(f"Submitting I{i} with {new_port}")

res = submit_and_extract(proj, out_dir)

print("Output at", res.output_dir.resolve())Decoding the Results

We first update our FASM to parse the input lines:

FASM with Input

class FASM:

def __init__(self, fasm_file: Path):

self.LUTS = defaultdict(BLE_CFG)

self.PPS_OUT = dict()

self.IRQ_OUT = dict()

self.OE = defaultdict(OESELn)

self.MUXS = defaultdict(MUX_CFG)

self.CLKDIV = CLKDIV.DIV_BY_1

self.COUNTER = COUNTER()

self.TIMR0_IN = None

with open(fasm_file, "r") as f:

for l in f.readlines():

if l.startswith("#"):

continue

if l.startswith("BLE_X"):

self.parse_ble(l)

continue

print(f"Unhandled line: {repr(l)}")

@staticmethod

def lo_to_ble(lo_str: str) -> str:

"""Convert 'LO_Y_X' to 'BLE_XY'."""

_, lo_y, lo_x = lo_str.split("_")

return f"BLE_X{int(lo_x) + 1}Y{int(lo_y) + 2}"

@staticmethod

def ble_to_lo(ble_str: str) -> str:

"""Convert 'BLE_XY' to 'LO_Y_X'."""

ble_x, ble_y = ble_str[5:].split("Y")

return f"LO_{int(ble_y) - 2}_{int(ble_x) - 1}"

def parse_ble(self, line):

parts = line.split(".")

try:

ble_sel = BLEXY.__members__[parts[0]]

if parts[1] == "BLE0":

if parts[2] == "FLOPSEL":

# ex: BLE_X1Y2.BLE0.FLOPSEL.DISABLE

self.LUTS[ble_sel].FLOPSEL = FLOPSEL.__members__[parts[3].strip()]

return

if parts[2] == "LUT":

# ex: BLE_X1Y2.BLE0.LUT.INIT[15:0] = 16'b1110101111110100

self.LUTS[ble_sel].LUT_CONFIG = parts[-1][-17:-1]

return

if parts[1].startswith("BLE0_LI"):

if parts[2].startswith("LO_"):

# ex. BLE_X3Y2.BLE0_LI0.LO_1_2

# Input from another BLE

ble_num = BLEXY.__members__[self.lo_to_ble(parts[2])].value

ble_id = f"CLB_BLE_{ble_num}"

else:

# ex. BLE_X3Y3.BLE0_LI0.CLBSWIN0

ble_id = parts[2].strip()

if parts[1][-1] == "0":

self.LUTS[ble_sel].LUT_I_A = LUT_IN_A.__members__[ble_id]

return

if parts[1][-1] == "1":

self.LUTS[ble_sel].LUT_I_B = LUT_IN_B.__members__[ble_id]

return

if parts[1][-1] == "2":

self.LUTS[ble_sel].LUT_I_C = LUT_IN_C.__members__[ble_id]

return

if parts[1][-1] == "3":

self.LUTS[ble_sel].LUT_I_D = LUT_IN_D.__members__[ble_id]

return

except Exception as e:

raise RuntimeError(f"Error parsing line '{line}'") from e

print(f"Unhandled ble line: {parts}")

returnNow to analyze what bits correspond with these changes we can track correlated bit changes. For example if we see a setting (like the LUT input) has a bit change from 0 to 1 and from a 1 to a 0 we can then look for correlated changes in the bitstream.

If we see a couple of bits in the input and output change, we can save a list of candidate bitstream bits for the setting bit. If we see it change again, we can identify which bitstream bits also changed and then find the intersection of bitstream changes.

The code is deceptively simple, but this powerful technique will serve us for the rest of our reverse engineering.

Note

Throughout the Python code, I use strings of bits (i.e., 10101) for bits because they are easier and clearer to manipulate in Python.

Bit Corr Tracker

class BitCorrelationTracker:

def __init__(self):

"""

A dictionary that maps:

setting_bit (hashable) -> set of candidate bitstream indices

"""

self.candidates_for_setting_bit = {}

def add_observation(

self,

bitstream_changes: list[tuple[int, bool]],

setting_changes: list[tuple[object, bool]],

):

"""

bitstream_changes:

A list of (bit_index, direction) for bits that changed in the bitstream.

direction = True means 1->0, direction = False means 0->1.

setting_changes:

A list of (setting_bit, direction) for bits that changed in the setting.

setting_bit can be any hashable (str, int, tuple, etc.).

direction = True means 1->0, direction = False means 0->1.

Raises:

ValueError if a new observation contradicts the existing candidates (i.e.,

it would force a candidate set to become empty).

"""

# Group bitstream bits by direction

bitstream_by_dir = {True: set(), False: set()}

for bit_idx, direction in bitstream_changes:

bitstream_by_dir[direction].add(bit_idx)

# Update candidate sets for each setting bit

for setting_bit, set_dir in setting_changes:

# All bitstream bits that moved in the same direction

possible_bits_now = bitstream_by_dir[set_dir]

# If we've never seen this setting bit before, just initialize:

if setting_bit not in self.candidates_for_setting_bit:

self.candidates_for_setting_bit[setting_bit] = set(possible_bits_now)

else: